簡要規格

万博Ansys Exalto後lv RLCk擷取使IC設計人員能夠準確預測電磁和基板耦合效應,以便在之前因為“太大而無法分析”的電路上進行簽核。擷取的模型可回貼至電路圖或串接電路,並支援所有電路模擬器。

万博Ansys Exalto是一種lv RLCk後擷取軟體解決方案,它會擷取集總電路寄生元件並產生精確的電氣,磁性和基板耦合模型,使IC設計人員能夠準確發現設計階層中不同區塊之間的不明串音干擾。Exalto。

万博Ansys Exalto後lv RLCk擷取使IC設計人員能夠準確預測電磁和基板耦合效應,以便在之前因為“太大而無法分析”的電路上進行簽核。擷取的模型可回貼至電路圖或串接電路,並支援所有電路模擬器。

英伟达(NVIDIA万博):

之前因為“太大而無法分析”的大型複雜電路,現在可以由Exalto的高速和高容量的矽裝置EM建模進行處理。

現代矽系統中射频與高速電路的激增,使電磁耦合成為一級效應,必須精確地建立模型,才能可靠地達成矽成功。中文:擷整整齐齐,整整齐齐。【中文译文】

【中文译文】其獨特的串接電路縮減方法使輸出串接電路極其小巧,從而減輕任何模擬問題。笨笨笨笨,笨笨笨笨,笨笨笨笨。因此,設計更小、更便宜,並有更多可靠的效能特性。

Exalto,。

万博Ansys Exalto藉由擷取集總電路寄生元件並產生精確的電氣,磁性和基板耦合模型,找到網目和階層區塊之間不明的串音干擾。Exalto可以在不同階層之間建立串音匯流排/模型,並執行多個“假設”情境,但無需變更您的電路圖。“。獨特的網表縮減方法將輸出網表減少 90% 以上。Exalto與所有lv工具連接,並使用針對部分或完整設計進行回貼的年代參數和RLCk寄生來補足RC擷取器。

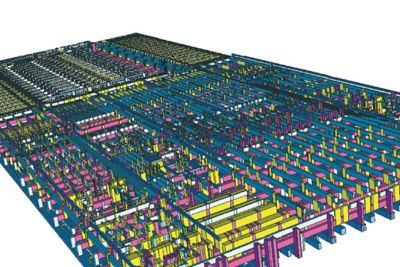

擷取集總電路寄生元件並為大型複雜矽電路的電氣、磁性和基板耦合產生精確的模型

產生適用於AC,諧波平衡和SP分析的被動,因果式直流準確年代參數模型,以及適用於暫態,散噪和雜訊分析的被動,因果,極精簡的RLCk網表模型。中文翻译:

万博Ansys Exalto . exe . exe . exe . exe . exe。它利用電容器和電晶體現有的晶圓廠特徵的裝置內模型,然後將總耦合電容集總到裝置終端。Exalto具有強大的容量和速度,即使是數千個裝置,也能擷取全部電容耦合。

万博Ansys Exalto、Ansys、Ansys、、、。這表示600 X 400嗯,高密度,7層金屬層電網的EM擷取需要幾分鐘時間;功率放大器中所有螺旋與主要數位線路之間的耦合模型需要幾秒鐘時間。

獨特的串接電路縮減方法使輸出串接電路變得極度精簡,與原生串接電路相比,元件和節點減少超過 90%。由於輸出串接電路太大,無法進行模擬,因此帶有附加高頻率(路)選項的傳統RC擷取器會出現電容瓶頸。

使用不同組的重要線路執行多個「假設」情境,但完全不用修改測試平台電路圖。

万博Ansys Exalto。“”“”“”“”Exalto“擷”“擷”。

齐格万博,齐格,齐格,齐格,齐格。因此,我們致力於遵循美國無障礙委員會(第508節),無障礙網頁內容規範(WCAG),自願性產品輔助工具範本(VPAT)當前格式等各項無障礙需求。